What is Setup and Hold Time in an FPGA?

Setup time and Hold time are important concepts to understand for every digital designer. This article explains what setup and hold times are and how they are used inside of an FPGA. This article assumes that the reader has at least a basic understanding of what a Flip-Flop is and how propagation delay affects designs.

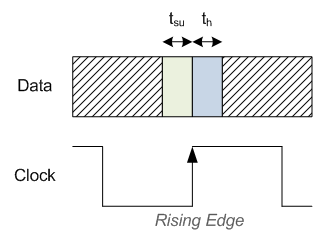

In the figure, the green area represents the tsu or Setup Time. The blue area represents the th or Hold Time. In these areas, the data into the Flip-Flop must be a stable 0 or a 1 or bad things will happen…

How does Setup and Hold time Relate to Propagation Delay and Clock Frequency?

Setup time, hold time, and propagation delay all affect your FPGA design timing. The FPGA tools will check to make sure that your design meets timing, which means that the clock is not running faster than the logic allows. The minimum amount of time allowed for your FPGA clock (its Period, which is represented by T) can be calculated. From this you can find the clock’s frequency, as frequency is the inverse of period (F=1/T). It is as follows:

tclk (min) = tsu + th + tp

Generally in your FPGA design, tsu and th are fixed for your Flip-Flops, so the only variable that you have control over is tp or the Propagation Delay. This delay represents how much stuff you’re trying to accomplish in one clock cycle. The more stuff you try to do, the longer tp will be, and the higher tclk (min) will be, which means that you will not be able to clock your FPGA design as quickly. This is the fundamental trade-off of FPGA designs. You are trading off how much stuff you can do in one clock cycle for the frequency of your clock. The two are inversely related… there’s no such thing as a free lunch!

What Happens if Setup and Hold Times Are Violated?

If your design has setup or hold time violations, the Flip-Flop output is not guaranteed to be stable. It could be zero, it could be one, it could be somewhere in the middle, it’s not known. This is called metastability. Metastability inside of an FPGA is not desirable, it can cause your FPGA to behave strangely. The physics behind metastability are interesting, you can read more about metastability here.

The main way that an FPGA designer finds out if they have violated setup or hold times is when running the FPGA through Place and Route. Place and Route is what happens when you take your VHDL or Verilog code and put it onto an FPGA. As a part of this process, the FPGA tools will take your design and run a timing analysis. It is in this timing analysis that you will see any timing errors, which are really just setup or hold time violations. How to fix these errors is beyond the scope of this article, but read the article on Propagation Delay to see how these timing errors can be fixed.

In conclusion, setup time and hold time is an important concept for an FPGA designer to understand. If these times are violated, the FPGA will not perform as expected!

Quiz Questions

Q. If a Flip-Flop has a 1 nanosecond (ns) setup time, what is the minimum amount of time that is required for the data to be stable prior to the clock?

A. 1 ns. This is the definition of setup time

Q. If two Flip-Flops have 1 ns setup time, 1 ns hold time, and 8 ns of propagation delay, what is the maximum frequency that this clock can run?

A. tclk (min) = tsu + th + tp. So tclk (min) = 1 ns + 1 ns + 8 ns = 10 ns. Remember that F=1/T, where T = 10 ns. F = 100 MHz.

Q. If you have a 50 MHz clock, 1 ns setup time, and 2 ns hold time, what will your design allow for its maximum propagation delay between two flip-flops?

A. tclk (min) = tsu + th + tp. Since F=1/T, tclk = 20 ns. So 20 ns = 1 ns + 2 ns + tp. tp = 17 ns

Q. If you have a situation where you have a 200 MHz clock and you have timing errors after running through Place and Route, what might you be able to do to fix this?

A. Timing errors are caused when you violate the equation tclk (min) = tsu + th + tp. Since setup time, hold time, and clock frequency are fixed, the only variable you can to play with is the propagation time. The simplest way to lower your propagation time is to cut down on the amount of stuff that you are trying to accomplish in 1 clock cycle. Divide your logic from 1 clock cycle into 2 clock cycles or more. For more information on this, read the article about propagation delay.

Maximum clock frequency does not depend on the hold time. There are two different equations for setup and hold violation, setup violation equation has time period of clock in it, while hold violation equation does not