What is Metastability in an FPGA?

How digital designers handle asynchronous events

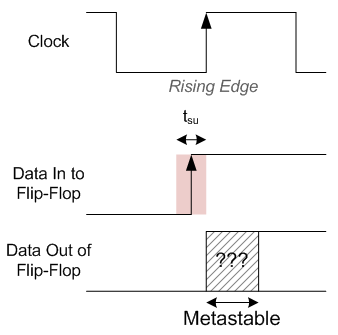

If you have ever tried to sample some input to your FPGA, such as a button press, or if you have had to cross clock domains, you have had to deal with Metastability. A metastable state is one in which the output of a Flip-Flop inside of your FPGA is unknown, or non-deterministic. When a metastable condition occurs, there is no way to tell if the output of your Flip-Flop is going to be a 1 or a 0. A metastable condition occurs when setup or hold times are violated.

How to Prevent Metastability

Most metastable conditions occur in one of two ways:

- You are sampling a signal external to the FPGA

- You are crossing clock domains

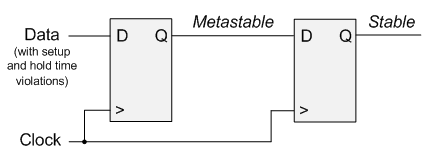

Both of these situations can be fixed the same way. Whenever you are encountering a situation that might introduce Metastability you can simply “double-flop” your data.

For further reading about Metastability, including the science behind it (and a lot of technical information about failure rates and such) Altera wrote a very detailed paper about it.

The issue of metastability is not at all about not knowing the reconvergence state. Because both 0 & 1 are correct answers for the Q output at the next clock cycle.

But you can state that metastability is not a good thing and that it is mitigated by using a double-Flops as you show.

This doesn’t change anything about not knowing the output but it statistically reduces (drastically) the probability that metastability will propagate in the fanout logic (MTBF)